提及“半导体”,我们的脑海中可能浮现的是深奥与遥不可及的科技概念。然而事实上,它已无处不在,融入了我们生活的点点滴滴:从手中的智能手机,到桌上的笔记本电脑,这些日常中不可或缺的物品,背后都离不开半导体的支持。

本文将着重介绍的是半导体封测行业。半导体封测,是在晶圆设计、制造完成之后,对测试合格的晶圆进行封装检测得到独立芯片的过程。它包括封装和测试两个主要环节,其中封装是将芯片按照产品型号及功能需求加工成独立的形式,而测试则是对封装后的芯片进行性能和质量检测。半导体封测是半导体生产流程中的最后一个环节,对于确保芯片的性能和质量至关重要。随着半导体产业的不断发展,封装技术也在不断进步,经历了多次重大革新。

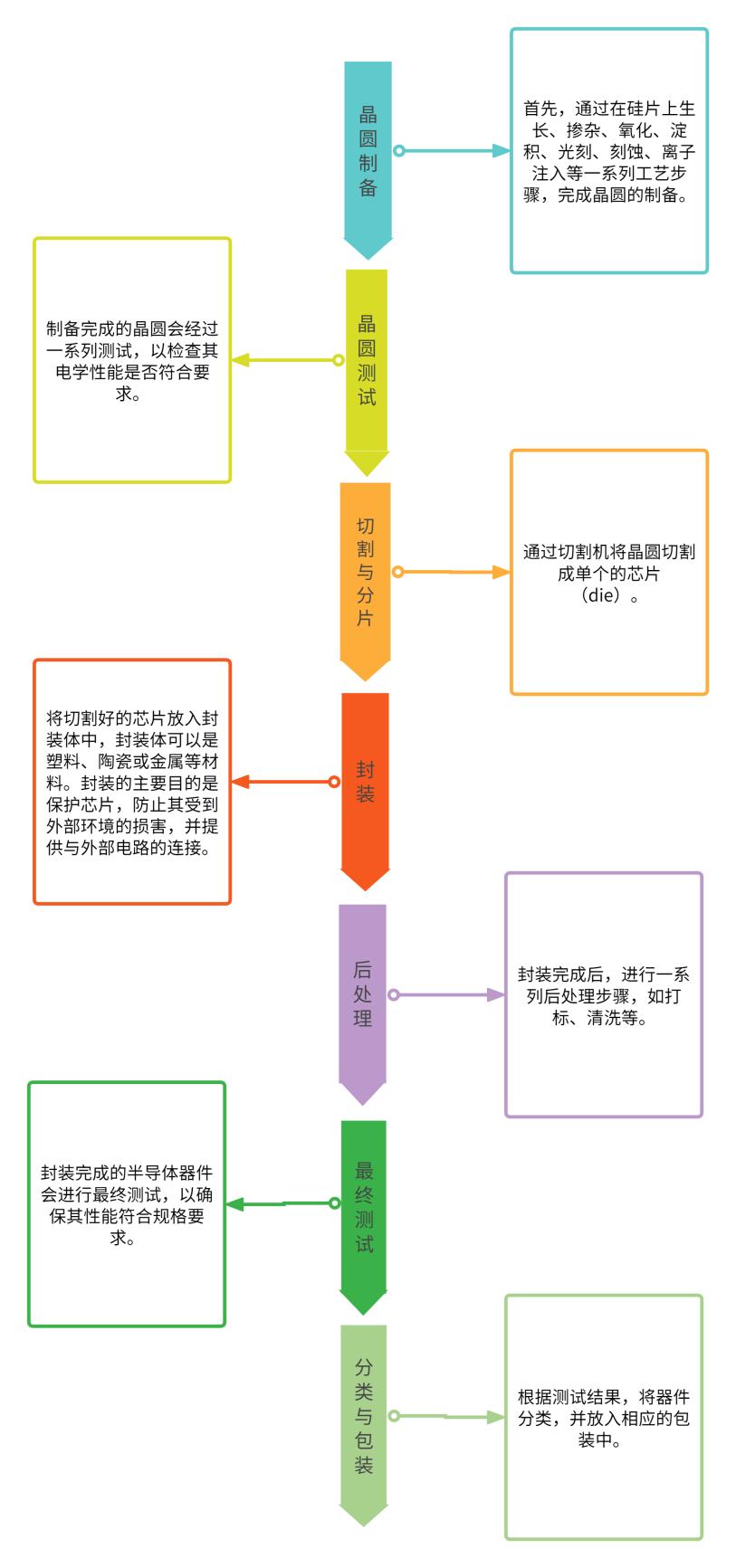

半导体封测的基本流程大致包括以下几个步骤:

以上是一个简化的流程,实际的半导体封测流程可能会因产品类型、封装类型以及制造商的工艺差异而有所不同,同时也衍生了大量的专业术语。接下来,本文将针对其中三个关键的制程进行介绍。

首先是CP测试。CP(Chip Probing)指的是晶圆测试,在整个芯片制作流程中处于晶圆制造和封装之间。晶圆(Wafer)制作完成之后,成千上万的裸DIE(未封装的芯片)规则的分布满整个Wafer。由于尚未进行划片封装,芯片的管脚全部裸露在外,这些极微小的管脚需要通过更细的探针(Probe)来与测试机台(Tester)连接。

为什么要进行CP测试?这是因为,在半导体制造过程中,Wafer制作完成后,由于生产工艺的复杂性和多种因素的影响,裸DIE中难免会出现一定数量的制造缺陷。这些缺陷可能导致芯片性能下降或功能失效。而CP测试的主要目的是对Wafer上的裸DIE进行全面检测,以识别和剔除那些存在制造缺陷的残次品。通过这一环节,我们可以显著提高出厂的良品率,从而降低后续封装和测试的成本。这不仅有助于提升整体生产效率,还为客户提供了更加可靠的产品。另外,在芯片封装过程中,有些管脚可能会被封装在内部,导致这些管脚的功能在封装后无法进行测试。

因此,CP测试成为了评估这些功能正常性的唯一机会。通过CP测试,我们可以确保所有关键功能在封装前都符合预期要求,从而避免潜在的性能问题。此外,一些先进的半导体公司还会根据CP测试的结果对芯片进行性能分级。这意味着,他们会根据芯片的性能差异将其分为不同的等级,并将这些产品投放到不同的市场。这种策略有助于满足不同客户的需求,并为公司创造更大的市场价值。

第二个重要制程则是封装(Assembly)。常见的封装形式有:

单列直插封装(SIP)

双列直插封装(DIP)

薄小型封装(TSOP)

塑料方形扁平封装(QFP)和塑料扁平组件封装(PFP)

插针网格阵列(PGA)

锯齿形直插封装(ZIP)

球栅阵列封装(BGA)

平面网格阵列封装(LGA)

塑料电极晶片载体(PLCC)

表面贴装器件(SMD)

无引脚晶片载体( LCC )

多晶片模组(MCM)

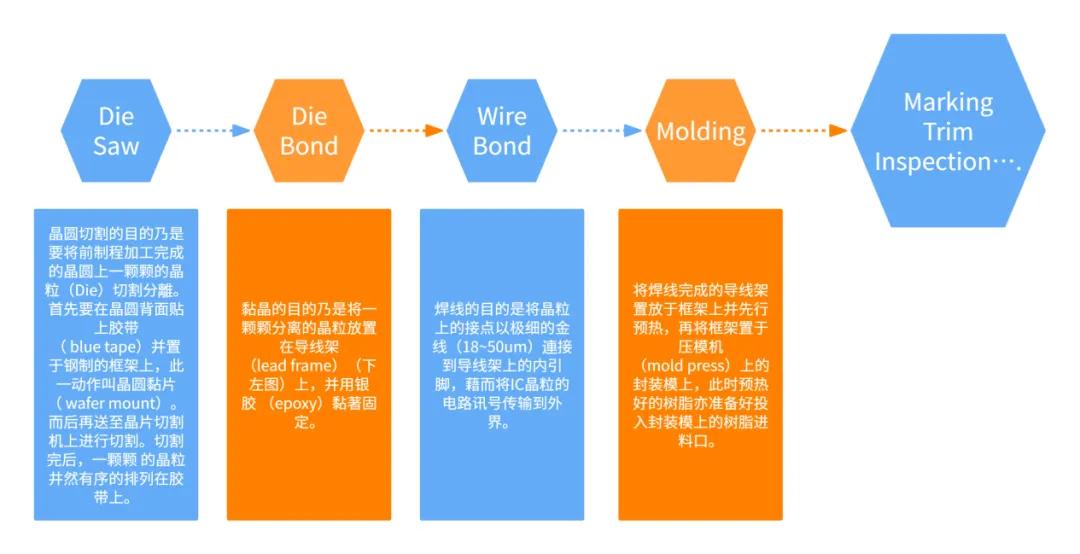

以下图举例说明一个Assembly制程的重点:

在这个过程中需要留意的是,Wafer转换成了Die,其单位也从PCS转换成了EA。比起成品,更应注重的是封装形式。

第三个要介绍的是FT测试,也称为Final Test,是半导体行业中的一个重要环节,主要对封装后的芯片进行最终的性能和功能测试。

在FT TEST中,测试设备会与芯片的引脚进行连接,并通过施加测试命令和采集输出信号来评估芯片在不同工作条件下的性能和功能的有效性。这些测试旨在确保芯片在实际应用中能够满足预期的性能标准,并具备稳定性和可靠性。FT TEST通常包括电学性能测试和功能验证等多个方面。电学性能测试主要关注芯片的电气特性,如电压、电流、电阻、电容等,以确保它们符合设计要求。功能验证则关注芯片的各项功能是否按照设计要求正常工作,包括逻辑功能测试、接口测试等。

此外,FT TEST还涉及对芯片进行环境测试和可靠性测试,以评估芯片在不同环境条件下的性能和稳定性。环境测试可能包括高温、低温、湿度、振动等条件下的测试,以确保芯片在各种实际使用环境中都能正常工作。可靠性测试则关注芯片的寿命和长期稳定性,通过长时间的老化测试、温度循环测试等来评估芯片的可靠性。

FT TEST是确保半导体产品质量的最后一道关卡,只有通过这一测试的芯片才会被出货。因此,FT TEST对于保障半导体元件的性能和可靠性至关重要。同时,随着半导体技术的不断发展,FT TEST也在不断演进和完善,以适应更复杂、更严格的测试需求。

其中,测试次数和测试程式往往由客户决定。

除了上述几个制程,半导体封测行业中还有其他一些重要的术语和概念,这些术语对于理解行业操作和流程也十分重要。例如:

Wafer bumping,即晶圆凸块,是倒装芯片(flip chip )或圆级封装(WLCSP, Wafer Level Chip Scale Package)必不可少的。凸块(Bumping)是一种先进的晶圆级工艺技术,在将晶圆(Wafer)切割成单个芯片之前,在整个晶圆形式的晶圆上形成由焊料制成的“凸块”(Bumps)或“球”(Balls)。这些“凸块”可以由共晶、无铅、高铅材料或晶圆上的铜柱(Cu pillar)组成,它们是将芯片(die)和基板(substrate)互连在一起形成一个单一封装的基本互连组件。

COF:Chip on Film。薄膜覆晶封装,是运用软性基板电路(flexible printed circuit film)作为封装晶片的载体,透过热压合将晶片上的金凸块(Gold Bump)与软性基板电路上的内引脚(Inner Lead)进行接合(Bonding)的技术。

COG:Chip on Glass。是一种将IC与玻璃基板相互连接的先进封装技术,液晶显示器(LCD Panel)模组工厂取得驱动IC后,利用覆晶(Flip Chip)技术以ACF导电胶(ACF全称Anisotropic Conductive Film,即异方性导电胶)为中间介面,将驱动IC上的凸块(Bump)与LCD面板上的ITO端点接合,主要应用于液晶显示器的驱动IC封装。

.....

由此可以看出,一种半导体产品的诞生,背后蕴藏着数百道精密工序的交织。其制程之复杂,主要体现在以下几点:

精细的工艺流程:半导体封测涉及多个精细的工艺流程,如芯片的切割、减薄、贴装、焊接、封装、测试等。每个步骤都需要精确控制各种参数,如温度、压力、时间等,以确保芯片的性能和可靠性。例如,在切割过程中,需要使用高精度的切割设备,将晶圆切割成独立的芯片,这要求切割精度极高,以避免损坏芯片或影响其性能。

严格的质量要求:半导体封测行业对产品的质量要求极为严格,因为任何微小的缺陷都可能导致芯片性能下降或失效。因此,在制程中需要进行多次质量检测和控制,如外观检查、电性能测试等,以确保每个芯片都符合规格要求。

高度自动化的生产线:由于半导体封测制程的复杂性和质量要求,生产线通常采用高度自动化的设备和系统。这些设备和系统需要具备高精度、高稳定性和高可靠性,以确保制程的稳定性和一致性。例如,自动化贴片机可以快速准确地将芯片贴装到基板上,自动化测试设备可以对芯片进行全面的电性能测试。

洁净的生产环境:半导体封测需要在高度洁净的环境中进行,以避免灰尘、颗粒物等污染对产品的影响。因此,生产线通常建在洁净室中,并采用各种空气净化技术,如高效过滤、层流送风等,以确保生产环境的洁净度。

相信敏锐的顾问们也已经察觉到,以上种种特点,给SAP项目的实施带来了诸多挑战,包括:

数据处理的复杂性:半导体封测制程涉及大量的数据,包括设备参数、工艺流程、质量检测结果、产品追溯信息等。这些数据需要在SAP系统中进行准确、高效的处理,以支持企业的生产管理和质量控制。然而,由于制程的复杂性,数据的收集、整合和分析变得异常困难,需要SAP顾问具备深厚的行业知识和技术背景。

业务流程的定制化需求:半导体封测企业的业务流程往往具有高度的定制化需求,因为不同企业的产品、设备、工艺等都有所不同。这使得SAP系统的实施需要进行大量的定制化配置和开发工作,以满足企业的特殊需求。顾问需要深入了解企业的业务流程和制程特点,提供针对性的解决方案。

质量控制和追溯的挑战:半导体封测行业对产品质量的要求极高,使得SAP系统需要发挥强大的质量管理和追溯功能,能够支持企业对产品进行全面的质量监控和追溯。这也是实施过程中的一大难点。

集成和协同的挑战:半导体封测行业的供应链涉及多个环节和多个企业,如原材料供应商、设备制造商、物流企业等。SAP系统需要实现与这些外部系统的集成和协同,以确保数据的共享和业务流程的顺畅进行。然而,由于半导体行业的特殊性,这些集成和协同工作往往面临诸多挑战,如数据格式不一致、系统接口不兼容等。

的确,半导体行业相关的SAP项目实施因其专业性和复杂性而显得颇具挑战性,这对于顾问而言无疑是一个不小的考验。然而,无论身处哪个行业,持续提升自身的专业素养和技能水平都是我们应当重视的任务。只有这样,方能在面对层出不穷的挑战和不断更新的技术时,保持敏锐的洞察力和应变能力,从而更好地适应并应对各种新情况和新问题。这既是我们职业成长的必经之路,也是为客户提供卓越服务的关键所在。

(文章转自微信公众号:爱记不记的记忆碎片,作者:姚静娴)